Описание

Altera плата ядра Cyclone EP4CE10 EP4CE10F17C8N циклонный уловитель IV FPGA макетная плата комплект все I/Os = OpenEP4CE10-C стандарт

Обзор

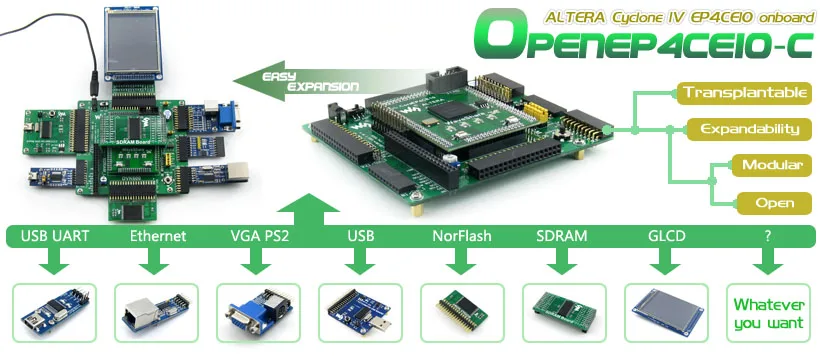

OpenEP4CE10-CЭто Плата развития FPGA, которая состоит из материнской платыDVK600И основная плата FPGACoreEP4CE10.

OpenEP4CE10-C поддерживает дополнительное расширение с различными дополнительными досками аксессуаров для специфического применения. Модульная и открытая конструкция делает его идеальным для запуска разработки приложений с циклонный уловитель IV серии FPGA устройств. OpenEP4CE10-C позволяет легко и быстро начать дизайн с процессором Nios II.

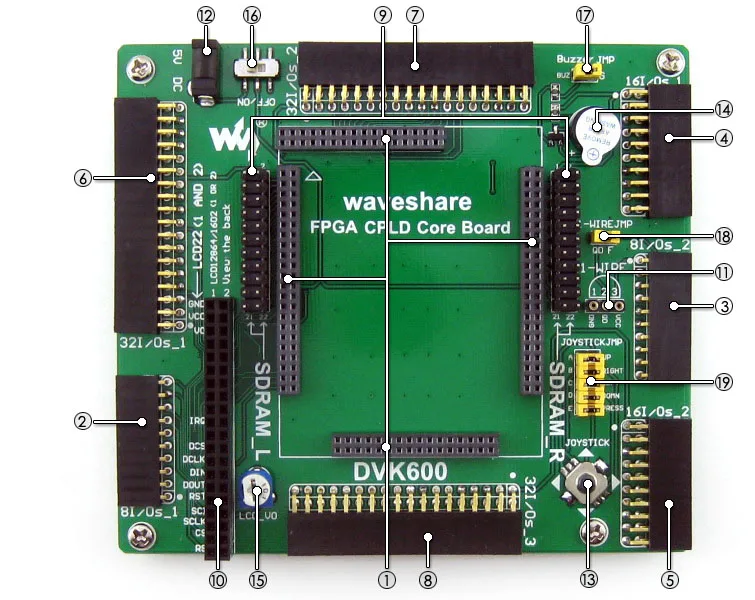

Что на материнской доске

Все интерфейсы ввода/вывода выше:

Может быть смоделирован как USART, I2C, SPI, PS/2 и т. д. Возможность вождения устройств, таких как FRAM, FLASH, USB, Ethernet и т. д.Для Джемперы 17-19:

Короткий Джемпер для подключения к I/Os, используемому в коде примера Откройте перемычку для подключения к другим разъемы в ассортименте с помощью перемычекDVK600 поддерживает широкий спектр различных картон для изготовления гильз, поэтому некоторые интерфейсы могут быть не подключены и бесполезны при подключении к определенной основной плате. Например, при подключении к Core3S500E/CoreEP2C8 не подключен «(8) 32I/Os_3».

Что на CoreEP4CE10

Фото

OpenEP4CE10-C макетная плата

OpenEP4CE10-C макетная плата

OpenEP4CE10-C макетная плата

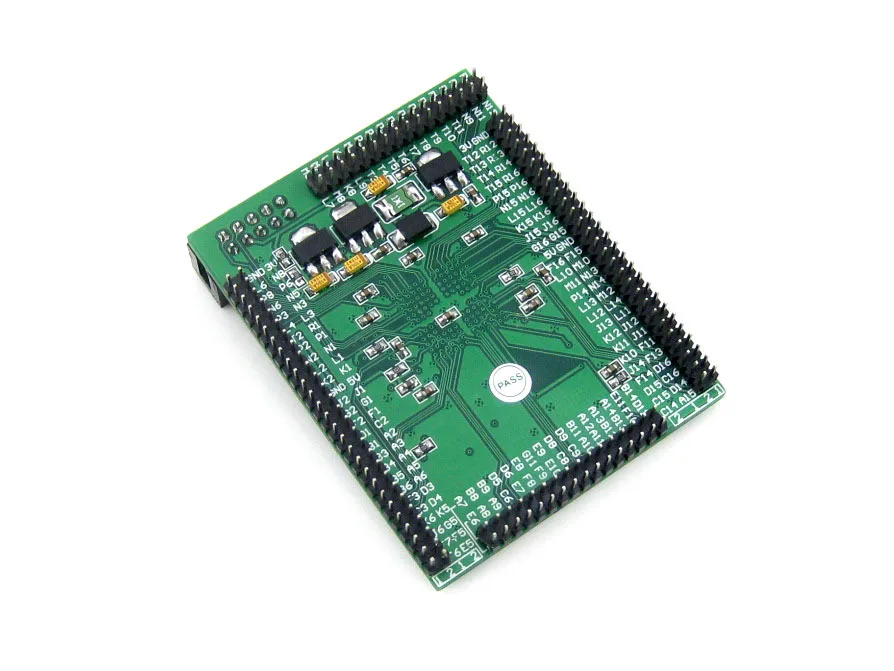

Материнская плата печатная плата для DVK600

FPGA основной плате CoreEP4CE10

FPGA основной плате CoreEP4CE10

Подключение к различные периферийные устройства

Подключение к 3,2 дюймовому сенсорному ЖК-дисплею

Подключение к LCD12864

Подключение к LCD1602

Подключение к RS232 доска

Подключение к RS485 доска

Подключение к USB плата UART

Подключение к 8 сегментный светодиодный плате

Подключение к 8 кнопочным кнопкам

Подключение к 5 IO клавиатуры

Подключение к 4x4 клавиатуры

Подключение к плата eeprom

Несколько периферийных устройств, подключенных к одному интерфейсу

Подключение к плата DataFlash

Подключение к плата Ethernet

Подключение к usb-плате CY7C68013A

Подключение к NRF24L01 RF Board

Подключение к плата запоминающего устройства Micro SD доска

Подключение к плате VGA PS2

Подключение к SDRAM доска

Подключение к SDRAM доска

Подключение к любой вспомогательной плате, которая вам нужна

Примечание: OpenEP4CE10-C не интегрирует любую функцию программирования/отладки, требуется программист/дебюгер.

Примеры

OpenEP4CE10-C FPGA development board поставляется с различными кодами для поддерживаемых периферийных устройств, которые позволяют быстро начать разработку собственного приложения.

| Периферийное устройство | Описание продукта: | Интерфейс | Verilog | VHDL | NIOS II C |

|---|---|---|---|---|---|

| S29GL128P | NorFLASH | 32I/Os | Y | ||

| AT24CXX | EEPROM | I2C | √ | √ | √ |

| FM24CXX | Фрам | I2C | √ | √ | √ |

| AT45DBXX | DATAFLASH | SPI | √ | ||

| SD карта | Флэш-память | SPI | √ | ||

| H57V1262GTR | SDRAM (синхронное динамическое ОЗУ) | Параллельный | √ | ||

| PCF8563 | РТК | I2C | √ | ||

| DS18B20 | Температура датчик | 1-проводной | √ | √ | √ |

| SP3232 | Последовательной связи | UART | √ | √ | √ |

| SP3485 | Последовательной связи | UART | √ | √ | √ |

| PL2303 | USB UART | UART | √ | √ | √ |

| FT245 | Usb-fifo | Параллельный | √ | ||

| CY7C68013A | USB устройство | Ввода/вывода | √ | ||

| ENC28J60 | Ethernet controller | SPI | √ | ||

| Зуммер | Звуковое устройство | 1I/O (PWM) | √ | √ | √ |

| PS/2 клавиатуры | Вход устройства | PS/2 | √ | √ | |

| Одной кнопки | Вход устройства | ---- | √ | √ | √ |

| 4x4 клавиатуры | Вход устройства | 8I/Os | √ | √ | √ |

| Джойстик | Вход устройства | 5I/Os | √ | √ | √ |

| Светодиодный | Дисплей устройства | ---- | √ | √ | √ |

| 8 сегментный светодиодный | Дисплей устройства | 13I/Os | √ | √ | √ |

| Монитор с видеографической матрицей | Дисплей устройства | VGA | √ | √ | |

| Персонаж ЖК-дисплей | Дисплей устройства | 11I/Os | √ | √ | |

| Графический ЖК-дисплей | Дисплей устройства | 11I/Os | √ | ||

| 3,2 дюймовый многоцветный ЖК + сенсорный экран | Устройство дисплея + Входное устройство | 32I/Os | √ |

Отладки/программирования Интерфейс

OpenEP4CE10-C FPGA development board интегрирует интерфейс JTAG для программирования/отладки.

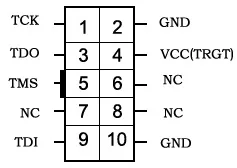

JTAG названия и описание сигнала

| Pin-код | Название сигнала | Описание продукта: |

|---|---|---|

| 1 | TCK | Часы сигнала |

| 2 | GND | Заземления сигнала |

| 3 | TDO | Данных от устройства |

| 4 | VCC (многоцел) | Цель блок питания |

| 5 | TMS | Джтаг государственного управления машиной |

| 6 | NC | Без подключения |

| 7 | NC | Без подключения |

| 8 | NC | Без подключения |

| 9 | TDI | Данные устройства |

| 10 | GND | Заземления сигнала |

Джтаг заголовок

Развития ресурсы

Сопутствующее программное обеспечение (Quaters II, NIOS II и т. д.) Код демонстрационной версии (Verilog, VHDL и NIOS II C) Схема (PDF) Документы разработки FPGA (таблицы данных и т. д.)Посылка содержит

Характеристики

- Тип демоплаты

- Рука

- Номер модели

- OpenEP4CE10-C Standard

- Бренд

- Waveshare

- Category

- ALTERA FPGA Development Board

- For use with

- EP4CE10 Development & Evaluation

- Onboard FPGA

- EP4CE10F17C8N (ALTERA Cyclone IV)

- Feature

- Open & Modular design, features various communication interfaces

- Onboard devices

- 1 x EPCS16SI8N, 4 x LED, 1 x User key, 1 x Joystick, 1 x Buzzer

- Communication interfaces

- 3 x LCD, 2 x 8I/Os, 2 x 16I/Os, 3 x 32I/Os

- Debugging/Programming

- supports JTAG

- RAM

- 414kb

- I/Os

- 164

- Package

- BGA256

- Demo Board Type

- Others